PCB板內阻抗指成品板內跡線的真實阻抗,與傳統的阻抗條(Coupon)不是一個概念。 由於PCB板內阻抗線與阻抗條阻抗線存在走線間距、走線寬度、走線所處環境、走線所處位置以及設計誤差等都會導致板內真實阻抗與阻抗條阻抗存在差异。 然而隨著當前線路板朝高密度、高多層、小體積的方向發展,客戶對阻抗控制要求越來越嚴格,控制精度要求也越來越高。 這種PCB板內阻抗與阻抗條阻抗存在的偏差可能會使高端客戶難以接受,囙此越來越多的客戶要求PCB廠家提供真實的PCB板內阻抗,而不是傳統的阻抗條。

PCB板內阻抗與阻抗條存在什麼差异?

1、雖然阻抗條與真實PCB板內阻抗線走線間距、走線寬度是一致的,但是阻抗條測試點的間距固定為2.54mm(為滿足測試探針間距),而板內真實走線的末端間距是可變的,隨著QFP、PLCC、BGA封裝的出現,一些晶片的引脚間距都遠小於2.54mm(即阻抗條測試點的間距)間距。

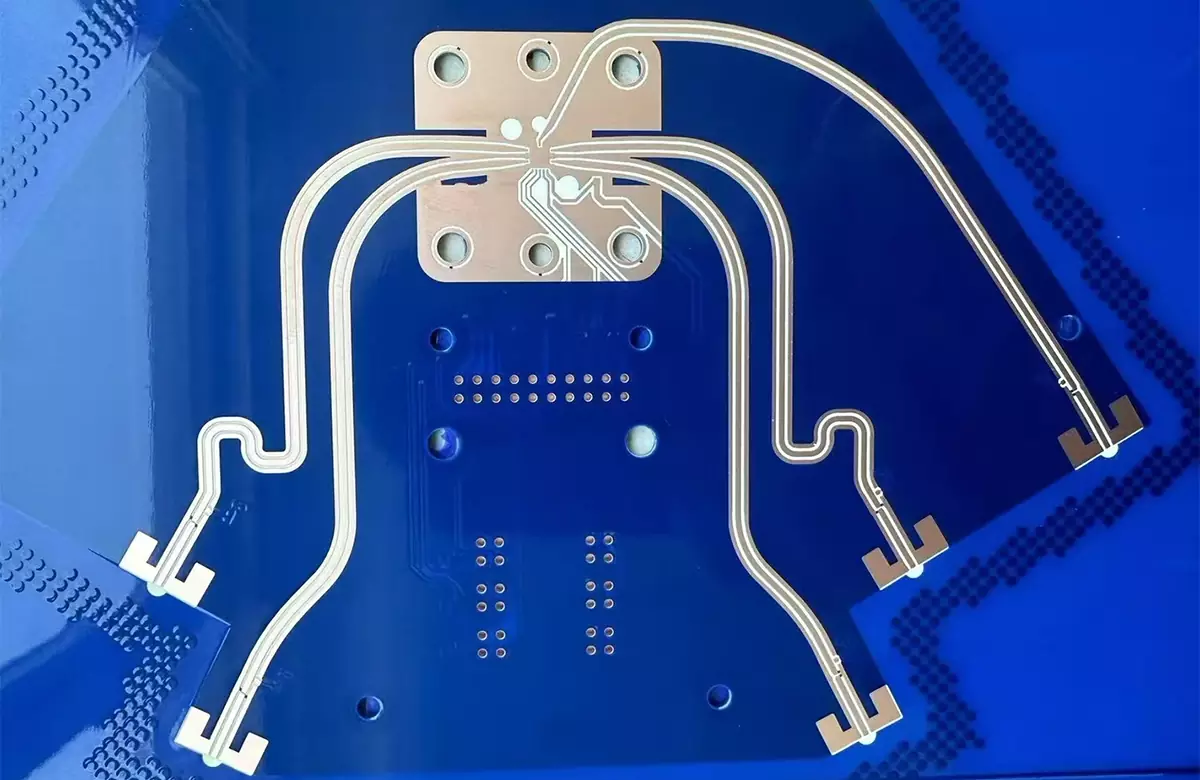

2、阻抗條走線是理想的直線,而板內真實走線往往是彎曲的、多樣的。 PCB設計人員和生產人員很容易將阻抗條的走線理想化,但是PCB板上的真實走線則會因為各種各樣的因素導致走線不規則化。

3、阻抗條和板內真實走線在整個PCB板上的位置不同。 阻抗條都位於PCB板中間或邊沿,在PCB板出廠時往往會被生產商去掉。 而板內真實走線的位置則是多樣的,有的在靠近板子的邊沿,有的位於板子的中央等。

4、PCB板內阻抗走線周圍一般分佈著過孔、焊盤、遮罩層等,而阻抗條走線周圍環境都比較單一。

PCB板內阻抗測試值的影響

1、阻抗條測試點間距阻抗條走線的間距不同,會導致測試點與走線之間帶來阻抗不連續。 而PCB板內的真實差分走線末端(即晶片的引脚)間距往往是與走線間距相等或者非常相近的。 由此會帶來阻抗測試結果的不同。

2、彎曲的走線與理想的走線所反映出來的阻抗變化是不一致的。 在走線彎曲轉折的地方特徵阻抗往往是不連續的,而阻抗條的理想化走線則不能反映由於走線彎曲所帶來的阻抗不連續現象。

3、阻抗條與真實的走線在PCB板上的位置不同。 現時的PCB板都採用多層走線的設計,在生產時需要經過壓制。 當PCB板在壓合工藝時,板子不同的位置所受到的壓力不可能做到一致,不同位置的介質層厚度有差异,這樣製成的PCB板在不同的位置上介電常數往往不相同,特徵阻抗也當然不同。

4、PCB板內阻抗受其周圍的過孔、焊盤、遮罩層等影響反映出來的阻抗是不連續的,而阻抗條因走線環境單一,不能反映阻抗真實變化情况。

可見阻抗條反映的阻抗值是不能完全反映PCB板內真實走線的真實特徵阻抗的。

PCB板

PCB板內阻抗測試的方法

TDR的基本原理階躍脈衝發生器發出一個快上升沿的階躍脈衝。 同時接收模組採集反射訊號的時域波形。 如果被測件的阻抗是連續的,則訊號沒有反射,如果有阻抗的變化,就會有訊號反射回來。 根據反射回波的時間可以判斷阻抗不連續點距接收端的距離,根據反射回來的幅度可以判斷相應點的阻抗變化。

隨著當前線路板朝高密度、高多層、小體積的方向發展,客戶對阻抗控制要求越來越嚴格,控制精度要求也越來越高,例如精度要求小於±5%。 PCB板內阻抗與阻抗條阻抗存在的偏差可能會超出控制精度要求,而且控制精度要求越高,採用阻抗條評估阻抗的風險就越大。

無論是PCB板的生產商還是高速電路設計者、製造者都希望能對PCB板內的真實高速差分走線直接進行TDR測試,獲得最準確的特徵阻抗資訊。

PCB板內阻抗測試的難點主要原因有以下兩個:

1、難以找到差分TDR探頭的接地點,高速PCB設計人員不會在設計高速差分走線時在走線的末端(即晶片引脚)附近放置固定間距的接地點。

2、差分走線的末端(即晶片的引脚或金手指或焊盤)間距是多變的,必需要一個間距可調的差分探頭來實現探測。