沒有阻抗控制的話,將引發相當大的訊號反射和訊號失真,導致設計失敗。 常見的訊號,如PCI匯流排、PCI-E匯流排、USB、以太網、DDR記憶體、LVDS訊號等,均需要進行阻抗控制。 阻抗控制最終需要通過PCB設計實現,對PCB工藝也提出更高要求,經過與PCB廠的溝通,並結合EDA軟件的使用,按照信號完整性要求去控制走線的阻抗。

以下幾種不同的走線管道都是可以通過計算得到對應的阻抗值。

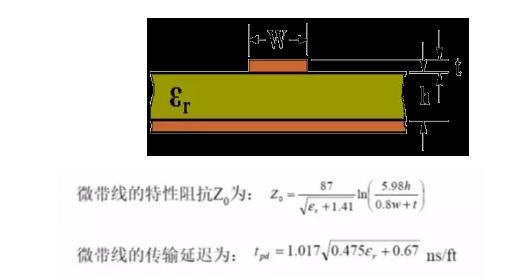

微帶線(microstrip line)

微帶線是由一根帶狀導線與地平面構成,中間是電介質。 微帶線的電介質的介電常數、線的寬度、及其與地平面的距離是可控的,則它的特性阻抗也是可控的,其精確度將在±5%之內。

微帶線說明

帶狀線(stripline)

帶狀線就是一條置於兩層導電平面之間的電介質中間的銅帶。 帶狀線的厚度和寬度,介質的介電常數,以及兩層接地平面的距離都是可控的,則線的特性阻抗也是可控的,且精度在10%之內。

帶狀線說明

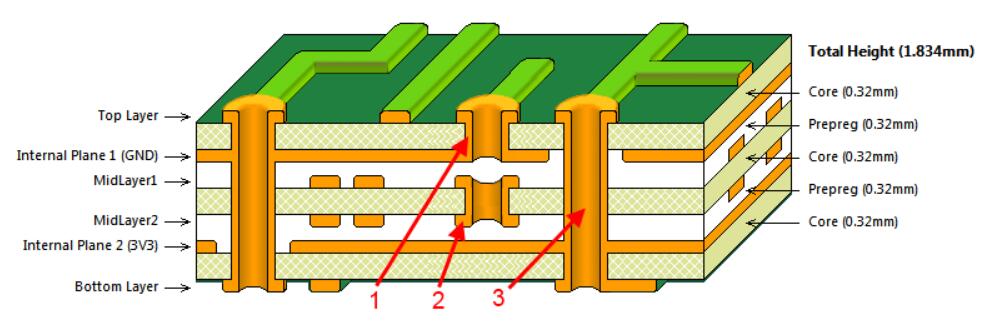

關於多層PCB的結構,為了很好地對PCB進行阻抗控制,首先要瞭解PCB的結構。

通常我們所說的多層PCB是由芯板和半固化片互相層疊壓合而成的,芯板是一種硬質的、有特定厚度的、兩面包銅的板材,是構成PCB的基礎資料。 而半固化片構成所謂的浸潤層,起到粘合芯板的作用,雖然也有一定的初始厚度,但是在壓制過程中其厚度會發生一些變化。

通常多層PCB最外面的兩個介質層都是浸潤層,在這兩層的外面使用單獨的銅箔層作為外層銅箔。 外層銅箔和內層銅箔的原始厚度規格,一般有0.5OZ、1OZ、2OZ(1OZ約為35um或1.4mil)三種,但經過一系列表面處理後,外層銅箔的最終厚度一般會新增將近1OZ左右。 內層銅箔即為芯板兩面的包銅,其最終厚度與原始厚度相差很小,但由於蝕刻的原因,一般會减少幾個um。

多層PCB的最外層是阻焊層,就是我們常說的綠漆,當然它也可以是黃色或者其它顏色。 阻焊層的厚度一般不太容易準確確定,在表面無銅箔的區域比有銅箔的區域要稍厚一些,但因為缺少了銅箔的厚度,所以銅箔還是顯得更突出,當我們用手指觸摸PCB表面時就能感覺到。

當製作某一特定厚度的PCB時,一方面要求合理地選擇各種資料的參數,另一方面,半固化片最終成型厚度也會比初始厚度小一些。 下麵是一個6層PCB疊層結構:

多層PCB疊層結構

PCB的參數

不同的PCB廠,PCB的參數會有細微的差异,通過與PCB廠技術支援的溝通,得到該PCB廠的一些參數數據.

表層銅箔:可以使用的表層銅箔資料厚度有三種:12um、18um和35um。 加工完成後的最終厚度大約是44um、50um和67um。

芯板:我們常用的板材是IT180,標準的FR-4,兩麵包銅,可選用的規格可與PCB廠家聯系確定。

半固化片:規格(原始厚度)有7628(0.185mm),2116(0.105mm),1080(0.075mm),3313(0.095mm),實際壓制完成後的厚度通常會比原始值小10-15um左右。 同一個浸潤層最多可以使用3個半固化片,而且3個半固化片的厚度不能都相同,最少可以只用一個半固化片,但有的廠家要求必須至少使用兩個。 如果半固化片的厚度不够,可以把芯板兩面的銅箔蝕刻掉,再在兩面用半固化片粘連,這樣可以實現較厚的浸潤層。

阻焊層:銅箔上面的阻焊層厚度C2≈8-10um,表面無銅箔區域的阻焊層厚度C1根據表面銅厚的不同而不同,當表面銅厚為45um時C1≈13-15um,當表面銅厚為70um時C1≈17-18um。

導線橫截面:我們會以為導線的橫截面是一個矩形,但實際上卻是一個梯形。 以TOP層為例,當銅箔厚度為1OZ時,梯形的上底邊比下底邊短1MIL。 比如線寬5MIL,那麼其上底邊約4MIL,下底邊5MIL,上下底邊的差异和銅厚有關。

介電常數:半固化片的介電常數與厚度有關:板材的介電常數與其所用的樹脂資料有關,FR4板材其介電常數為4.2-4.7,並且隨著頻率的新增會减小。

介質損耗因數:電介質資料在交變電場作用下,由於發熱而消耗的能量稱之謂介質損耗,通常以介質損耗因數tan δ 表示。 生益S1141的典型值為0.015。

線路公差:能確保加工的最小線寬和線距:3mil/3mil。

阻抗計算的工具簡介

當我們瞭解了多層PCB的結構並掌握了所需要的參數後,就可以通過EDA軟件來計算阻抗。 可以使用Polar SI9000,這是一個很好的計算特徵阻抗的工具,現在很多PCB廠都在用這個軟件。

無論是差分線還是單端線,當計算內層訊號的特徵阻抗時,你會發現Polar SI9000的計算結果與Allegro僅存在著微小的差距,這跟一些細節上的處理有關,比如說導線橫截面的形狀。 但如果是計算表層訊號的特徵阻抗,我建議你選擇Coated模型,而不是Surface模型,因為這類模型考慮了阻焊層的存在,所以結果會更準確。 下圖是用Polar SI9000計算在考慮阻焊層的情况下表層差分線阻抗的部分截圖:

由於阻焊層的厚度不易控制,所以也可以根據板廠的建議,使用一個近似的辦法:在Surface模型計算的結果上减去一個特定的值,建議差分阻抗减去8歐姆,單端阻抗减去2歐姆。

差分對走線的PCB要求

1、確定走線模式、參數及阻抗計算。 差分對走線分外層微帶線差分模式和內層帶狀線差分模式兩種,通過合理設定參數,阻抗可利用相關阻抗計算軟件(如POLAR-SI9000)計算也可利用阻抗計算公式計算。

2、走平行等距線。 確定走線線寬及間距,在走線時要嚴格按照計算出的線寬和間距,兩線間距要一直保持不變,也就是要保持平行。 平行的管道有兩種:一種為兩條線走在同一線層(side-by-side),另一種為兩條線走在上下相兩層(over-under)。 一般儘量避免使用後者即層間差分訊號,因為在PCB板的實際加工過程中,由於層疊之間的層壓對準精度大大低於同層蝕刻精度,以及層壓過程中的介質流失,不能保證差分線的間距等於層間介質厚度,會造成層間差分對的差分阻抗變化。 困此建議儘量使用同層內的差分。

以上是我們對如何對PCB進行阻抗控制的說明,以及多層PCB疊層結構還有影響阻抗的參數說明。