電路基板都要用到銅箔,在高可靠性的應用中,選擇恰當的銅箔基板可以為電路提供最佳效能。

銅箔有多種不同的類型,比如存在重量(厚度)的差异,以及不同銅箔之間的特性也各不相同。 瞭解它們之間的差异,可以幫助工程師在不同的應用環境下,選擇正確的銅箔類型。

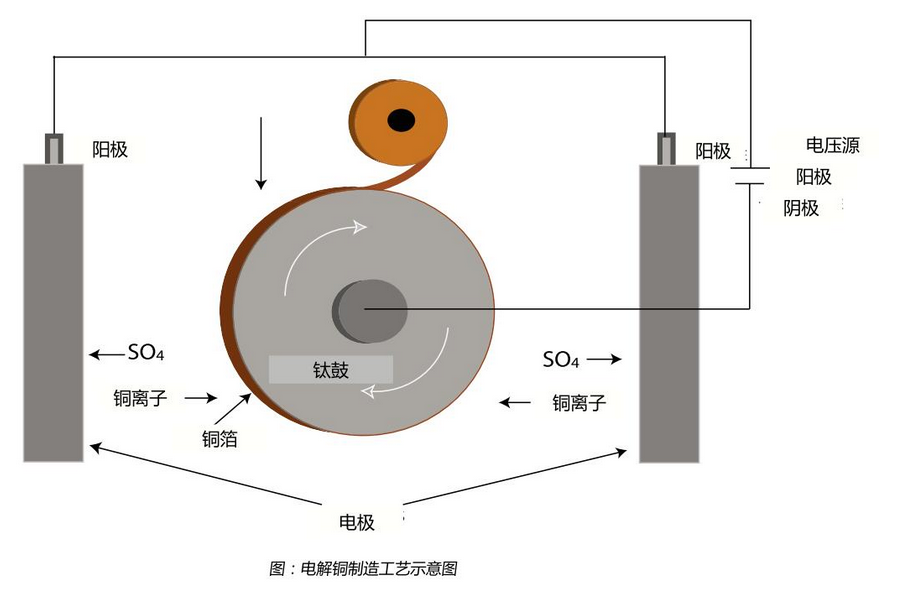

銅箔制造技術之電解銅箔

電解銅箔的制造技術中,銅箔是從含銅離子化學溶液中沉積到旋轉的鈦鼓上形成的。 鈦鼓與直流電壓源相連,其中電源陰極連接到鈦鼓上,陽極浸沒在銅電解質溶液中。 當施加電壓時,鈦鼓以非常慢的諫度旋轉,銅溶液裡面的銅離子在電流的牽引下就會慢慢地沉積到鈦鼓的陰極表面。 鈦鼓的內側銅表面是較光滑的,而另一側的銅表面相對而言較粗糙。 鈦鼓轉動速度越慢,沉積的銅就會越厚,反之亦然。 銅箔的光滑面和粗糙面在經過不同的處理流程後,就可以適用於印刷電路板的製作了。 銅箔經過工藝處理後,可以增强銅與介質資料之間的結合力。 另一個優點是,可以減緩銅的氧化來起到抗變色的作用。

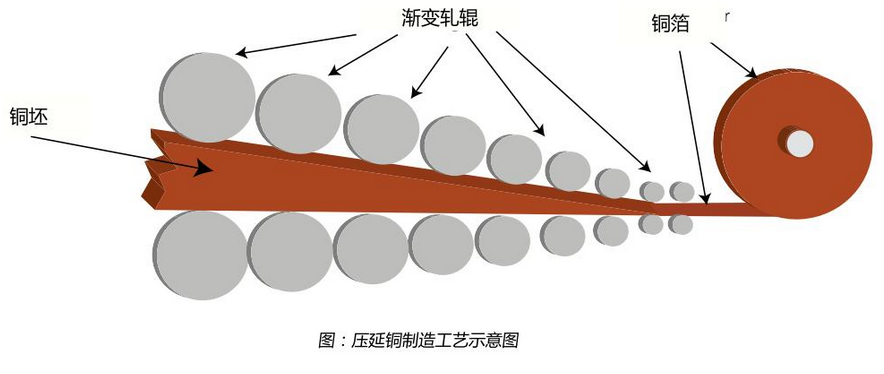

銅箔製造技術之壓延銅箔

銅箔製造技術之壓延銅箔壓延銅箔是通過連續冷軋操作製成的。 從純銅坯料開始不斷碾軋縮減厚度並延長長度。 其表面的光滑程度取决於軋機的狀態。

銅箔電阻在電解銅箔的粗糙面塗覆金屬或合金,起到電阻層的作用。 接下來就可以用鎳顆粒粗化電阻層。 反轉銅箔和Lo Pro銅箔反轉銅箔是將電解銅箈的光滑面進行處理。 其過程是在光湑表面迸行-層薄處理,將光湑表面變粗糙。 目的是提髙銅箔與電介質之間的結合力,並且新增銅箔的耐腐蝕性。 在與介質資料結合壓合成多層板時,經過處理的銅箔表面將被層壓到電介質資料上處理以後的銅面仍會比較光滑,而粗糙面仍舊非常粗糙。 這是相對於標準電解銅的一個優勢,在電路加工壓幹膜前之前,外層的粗糙面不需要再做其它仼何機械或化學方面的處理。 因為它本身的粗糙度已經足以保證幹膜的附著力。 對於Loro銅箔,就是在反轉銅箔的處理面新增了一層薄薄的粘合劑,形成了一個粘合性增强的實體層。 與反轉銅箈-樣,經過粘合劑處理的面將與介電層相壓合,可以獲得更好的結合力。 羅傑斯的R○4000系列資料就是採用Loro銅箈的線路多層板

銅箔電阻

在電解銅箔的粗糙面塗覆金屬或合金,起到電阻層的作用。 接下來就可以用鎳顆粒粗化電阻層。

反轉銅箔和Lo Pro銅箔

反轉銅箔是將電解銅箈的光滑面進行處理。 其過程是在光湑表面迸行-層薄處理,將光湑表面變粗糙。 目的是提髙銅箔與電介質之間的結合力,並且新增銅箔的耐腐蝕性。 在與介質資料結合壓合成多層板時,經過處理的銅箔表面將被層壓到電介質資料上處理以後的銅面仍會比較光滑,而粗糙面仍舊非常粗糙。 這是相對於標準電解銅的一個優勢,在電路加工壓幹膜前之前,外層的粗糙面不需要再做其它仼何機械或化學方面的處理。 因為它本身的粗糙度已經足以保證幹膜的附著力。

對於Loro銅箔,就是在反轉銅箔的處理面新增了一層薄薄的粘合劑,形成了一個粘合性增强的實體層。 與反轉銅箈-樣,經過粘合劑處理的面將與介電層相壓合,可以獲得更好的結合力。 羅傑斯的R○4000系列資料就是採用Loro銅箈的線路多層板。

晶體結構電解銅的昰體顆粒在銅箔的Z軸上縱冋生長。 通常,電解銅箈的截面寳易看到具有尖樁柵欄的外觀,並具有垂直於銅箈平面的長昰體邊界。 壓延銅的銅皛體結枃在由銅塊碾軋操作過程中被破壞了。 它們的昰體結枃比電解銅昰體小,具有不規則的球形形狀並且幾乎平行於銅箔表面。

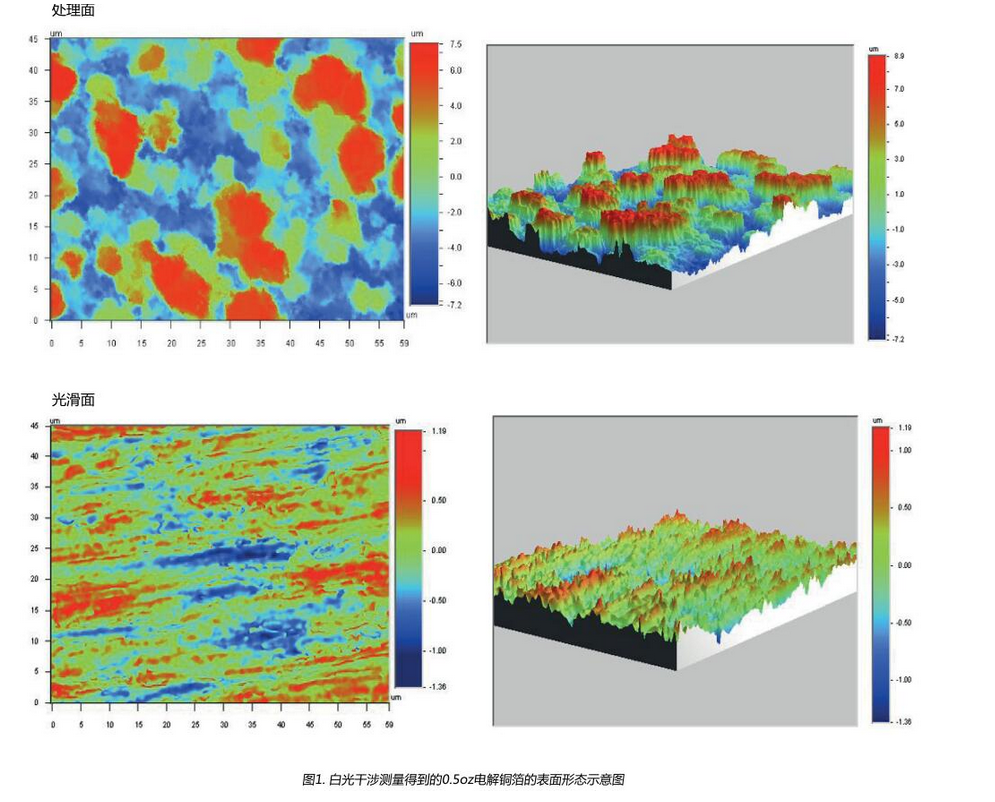

銅箔粗糙度量測

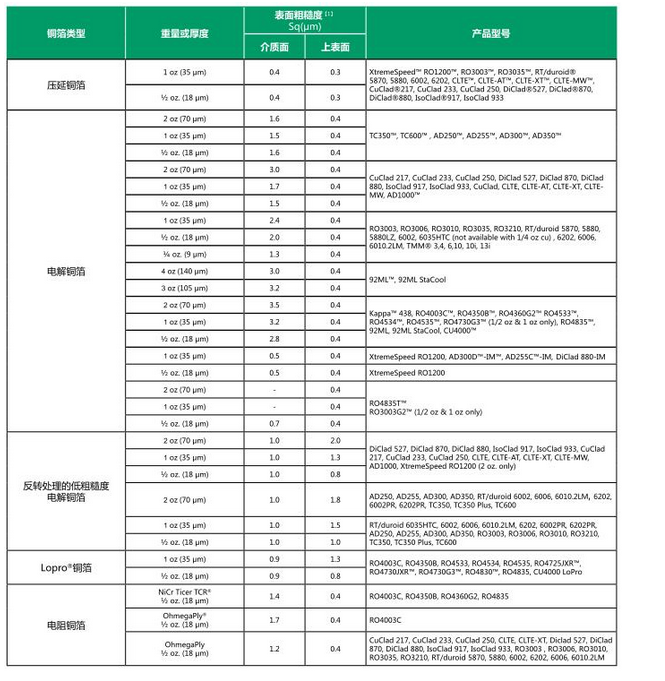

銅箔表面的粗糙度可以通過機械的或光學的方法來量測。 許多文獻中都提到“Rz〃(峰穀)值,這是因為它通過機械管道的測量儀來量測得到。然而,根據我們的經驗,通過非接觸式白光干涉測量法量測到的銅箔表面的Sq(RMS) 粗糙度與實際的導體損耗更一致。 圖1顯示了使用非接觸式白光干涉儀量測的羅傑斯PTFE和TMM多層板上使用的0.5oz電解銅箔的表面特徵。 錶1顯示了羅傑斯層壓資料上使用的銅箔類型以及典型的粗糙度資訊。 最新的一項硏究(參考文獻7)表明,“上表面”粗糙度與介質面具有完全不同的結構,它對傳輸線導體損耗幾乎沒有影響。

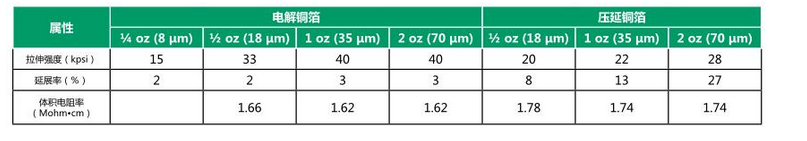

如下錶所示,是使用光學測量儀測得不同厚度的電解銅箔和壓延銅箔的粗糙度數據。 錶中還提到了羅傑斯的哪種多層板使用了哪種的銅箔類型。 可以看到,壓延銅是最光滑的銅箔。

高頻多層電路板的電效能

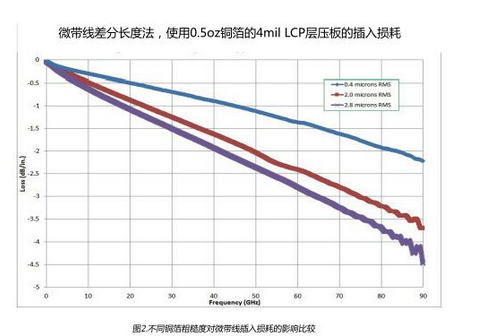

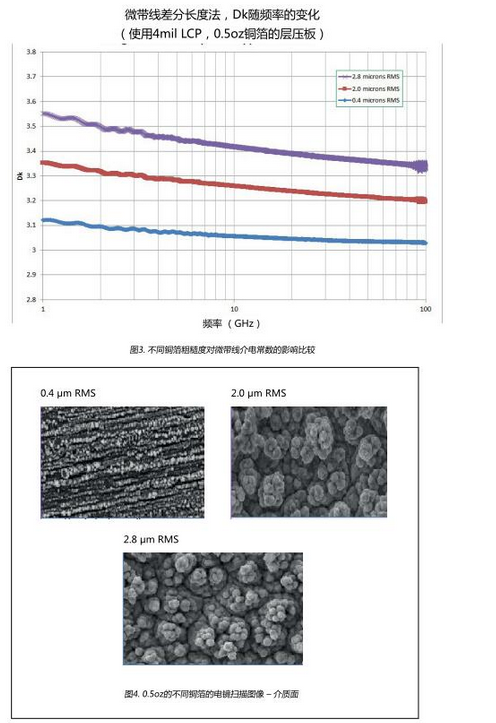

在波導中,導體的表面粗糙度對導體損耗有著顯著的影響,這一點在微波工程的早期就已經被人們所熟知。 1949年,S.P.Morgan(參考文獻1)發表的數值模擬結果表明導體表面粗糙度可導致導體損耗成倍新增。 Hammerstad和Jensen(參考文獻2)將Morgan的模型和資料與微帶設計方法結合起來。 H αυ 的模型成為計算表面粗糙度對導體損耗影響的“教科書〃(參考文獻3)式的方法。隨著使用更髙頻率和更薄多層板,硏究發現H α 模型明顯低估了表面粗糙度對導體損耗的影響(參考文獻5,6)Hal- Huray“模型(參考文獻4)是從“第一原則”分析發展而來,最近已經被商業類比設計軟體採用。根據我們的經驗,通過適當調整輸入參數,“Ha‖l- Huray”模型可以更準確預測不同多層板厚度和頻率範圍內的導體損耗。“Hal- Huray” 模型已被納入羅傑斯公司的阻抗和損耗小算盘軟體(MwM)中。 我們現時正致力於開發最好的“HalHuray”輸入參數來類比羅傑斯的多層板效能。 請線上査看羅傑斯官網的攴持中心或聯系您所在地區的羅傑斯銷售工程師來獲取最新資訊。 羅傑斯對銅箔的硏究(參考文獻5,6,7)還錶眀,銅箔粗糙度會影響傳播常數,比較粗糙的銅箔表面會導致有效介電常數明顯增加。 圖3顯示了在4mi液晶聚合物多層板(LCP)上,分別使用Sq值在0.4um到28um的銅箔,其50歐姆傳輸線的介電常數情况。 可以看到具有最大粗糙度銅箔的電路的Dk新增近10‰%。 在“Hall-huray“模型中沒有考慮到銅箔粗糙程度對相位回應的影響銅箔表面粗糙度對插入損耗的影響非常明顯(如圖2)。在90GHz下,由4mi厚的液晶聚合物(LCP)多層板、壓延銅箔(藍線)製成的50歐姆傳輸線的插入損耗汋2.2dB/i η ch,該效能幾乎與完全光滑的銅箈導體的模型完全相同。 在相同的基板上採用標準電解銅箔,其Sq值為2.oum,插入損耗增大為3.7dB/inch。 圖4顯示了圖2中所示資料的導體的銅箔表面粗糙度的形態。

多層板的機械效能A.抗熱衝擊性在某些快速熱回圈的極端條件下,電解銅箔在較窄的導體中可能岀現熱應力裂紋。 但在同樣的條件下,壓延銅的抗裂性會有顯著的提高。 雖然電解銅箈有更大的拉伸强度和延展性,但壓延銅箔在達到永久變形前具有更好的彈性延展性。 B.銅箔結合力由於樹脂與金屬的粘合主要是靠杋械粘合,囙此多層板的銅箔結合力大小與處理過的銅箈表面粗糙度直接相關。 C.帶狀線結構的粘合(聚四氟乙烯基板)SEM照片顯示了不同銅箔類型和銅箔蝕刻後的介質表面之間的形貌和粗糙度的差异。 如果電路板是粘接的,則對於電解銅箈而言,無需對電介質表面進行鈉或等離子處理,但前提是要注意保護好表面。 然而,對於壓延銅電路板,由於其較小的銅箔表面粗糙度將導致比較差的機械結合力,囙此表面處理對於可靠的粘接組裝是必要的。 附錄兩種不同類型銅箈的不同製造方法導致了電力和機械效能的差异。 錶2中列出了其主要差异。

以上是分享電路板材料的銅箔介紹,注意電解銅箔和壓延銅箔有不同的性能。