串擾是指由於平行線較長而引起PCB上不同網絡之間的相互干擾,主要是由於平行線之間的分佈電容和電感。

克服串擾的主要措施是:

1、新增平行線間距,遵循3W原則。

2、在平行線之間插入接地隔離器。

3、减少佈線層與地平面之間的距離。

3 W規則

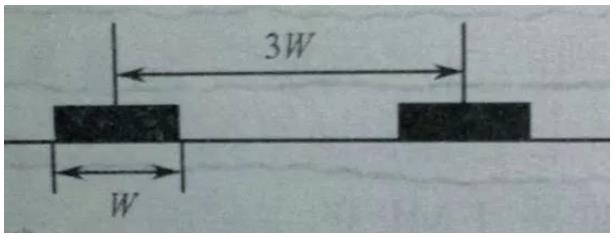

為了减少線間串擾,線間距要足够大。 當線中心間距不小於3倍線寬時,可以保持70%的電場互不干擾,稱為3W原則。 要達到98%的電場互不干擾,可以使用10W的間距。

在實際PCB設計中,3W原則不能完全滿足避免串擾的要求。

根據實際經驗,如果沒有遮罩地,上面印的訊號線之間的距離要大於LCM,防止串擾,所以在PCB電路佈線中,需要雜訊訊號(如時鐘線)和雜訊訊號,而EFTlB,“髒”“乾淨”等ESD干擾需要線上保護,不僅要強制使用3W原則,還要對地包進行遮罩處理,以防止串擾的發生。

此外,為避免串擾在PCB,PCB設計和佈局,應考慮為例如:

1、按功能劃分邏輯器件系列,嚴格控制匯流排結構。

2、儘量減少組件之間的物理距離。

3、高速訊號線及元器件(如晶振)應遠離I/()互連介面等易受數據干擾和耦合影響的區域。

4、為高速線路提供正確的接線端子。

5、避免長距離平行佈線,並在佈線之間提供足够的間距,以儘量減少電感耦合。

6、相鄰層(微帶或條帶)上的佈線應相互垂直,以防止層間電容耦合。

7、减少訊號與地平面之間的距離。

8、分離隔離高雜訊發射源(時鐘、I/O、高速互連),不同訊號分佈在不同層。

9、儘量新增訊號線之間的距離,可以有效降低電容串擾。

10、降低引線電感,避免在電路中使用阻抗很高的負載和阻抗很低的負載,儘量使類比電路的負載阻抗穩定在loQ~lokQ之間。 因為高阻抗負載會新增容性串擾,當使用非常高的阻抗負載時,由於工作電壓高,電容串擾會新增,而當使用非常低阻抗負載時,由於工作電流大,電感串擾會新增。

11、在PCB內層鋪設高速週期信號。

12、採用阻抗匹配科技,保證BT訊號的完整性,防止過沖。

13、注意上升沿快(tr≤3ns)的訊號,進行接地抗串擾處理,在PCB邊緣佈置一些受EFTlB或ESD干擾而未被過濾的訊號線。

14、盡可能使用地平面。 使用地平面的訊號線會比不使用地平面的訊號線衰减15~20dB。

15、訊號高頻訊號和敏感訊號都包含在地面處理中,雙面板採用地面覆蓋科技,衰减10~15dB。

16、使用平衡線、遮罩線或同軸線。

17、過濾騷擾訊號線和敏感線。

18、合理設定層數和佈線,合理設定佈線層數和佈線間距,减少並行訊號長度,减少訊號層與平面層間距,新增訊號線間距,减少長度平行訊號線(在金鑰長度範圍內)可以有效减少串擾。

3W原則是一種防止串擾的一種方法,該方法僅作為一種參攷,並作為理解如何防止串擾的一種啟發。 實際PCB設計中,3W原則並不能完全滿足避免串擾的要求。 按實踐經驗,如果沒有遮罩地線的話,PCB訊號線之間大於lcm以上的距離才能很好地防止串擾,囙此在PCB線路佈線時,就需要在雜訊源訊號(如時鐘走線)與非雜訊源訊號線之間,及受EFT、ESD等干擾的“髒“線與需要保護的“乾淨”線之間,不但要強制使用3W原則,而且還要進行遮罩地線包地處理, 以防止串擾的發生。 另外,不是所有的PCB上的走線都必須遵照3W佈線原則。 使用這一設計指導原則,在PCB佈線前,决定哪些條走線必須使用3W原則是十分重要的。