在試驗檢查晶片長期貯存條件下,高溫和時間對器件的影響。 本規範適用於量產晶片驗證測試階段的HAST測試需求,僅針對非密封封裝(塑膠封裝),帶偏置(bHAST)和不帶偏置(uHAST)的測試。

在試驗通過溫度、濕度、大氣壓力加速條件,評估非密封封裝器件在上電狀態下,在高溫、高壓、潮濕環境中的可靠性。 它採用了嚴格的溫度,濕度,大氣壓、電壓條件,該條件會加速水分滲透到資料內部與金屬導體之間的電化學反應。

HAST測試標準

JESD22-A110E HAST測試標準

JESD471 可靠性總體標準

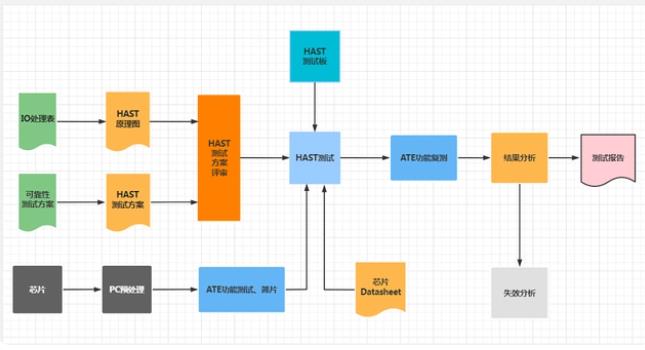

HAST測試流程

HAST測試條件

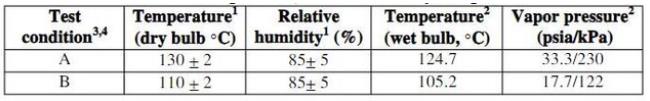

1、溫度、濕度、氣壓、測試時間HAST試驗條件如下表所示:

通常選擇HAST高壓加速老化試驗箱RK-HAST-350,即:130℃、85%RH、230KPa大氣壓,96hour測試時間。

測試過程中,建議調試階段監控晶片殼溫、功耗數據推算晶片結溫,要保證結溫不能過高,並在測試過程中定期記錄。 結溫推算方法參攷《HTOL測試技術規範》。

如果殼溫與環溫差值或者功耗滿足下錶三種關係時,特別是當殼溫與環溫差值超過10℃時,需考慮週期性的電壓拉偏策略。

注意測試起始時間是從環境條件達到規定條件後開始計算。 結束時間為開始降溫降壓操作的時間點

2、電拉偏

uHAST測試不帶電壓拉偏,不需要關注該節。

bHAST需要帶電壓拉偏,遵循以下原則:

所有電源上電,電壓:推薦操作範圍電壓(Maximum Recommended Operating Conditions)

晶片功耗小(數位部分不翻轉、輸入晶振短接、其他降功耗方法)。

輸入管脚在輸入電壓允許範圍內拉高。

其他管脚,如時鐘端、復位端、輸出管脚在輸出範圍內隨機拉高或者拉低。

HAST設備

高溫、高壓、濕度控制試驗箱(HAST高壓加速老化試驗箱)-溫度、濕度、氣壓强度範圍可控,測試時間可控。

失效判據

ATE\功能篩片有功能失效、效能异常。

HAST測試注意事項

HAST測試過程要求每天記錄電源電壓、電流、環境溫度、殼溫(推算結溫)等關鍵數據。

注意晶片內部類比電路是否有上電默認開啟的模塊,這樣的模塊會導致靜態電流太大,引起其他機制的失效。

HAST調試過程注意,考慮到較大的電流引起壓降,電壓等的記錄應該是到板電壓,而不是電源源端電壓。

HAST調試過程注意,室溫條件下的電源電壓與規定要求下的電源電壓不同,可以在室溫下初調,待試驗環境到達HAST設定條件後做終調試。