FPGA多數據採集卡PCBA優勢

FPGA由於其時鐘頻率高、內部延遲小、速度快、效率高、組合靈活等特點,在DSP和MCU之間的高速數據採集方面具有無可比擬的優勢。

FPGA多數據採集卡數據採集系統採用模塊化設計結構,由4個模塊組成。 每個採集模塊可以互換或靈活增加。 模塊通過三路連接器連接。 傳感器信號和422串口信號輸入相應模塊,主控模塊控制統一分幀並傳輸至雙備份存儲器。 設計方案靈活,易於控制,具有很好的實用價值。

FPGA PCB

FPGA多數據採集卡PCBA優勢

系統硬件設計

數據採集記錄系統由一張主控卡和三張數據採集卡組成。主控卡是數據採集系統的核心部分,主要包括地面測控站長線通訊、各數據採集卡的數據傳輸控制、數據轉發、存儲控制等功能。三塊數據採集卡可採集72路模擬信號。每個數據採集卡中的FPGA根據地址跳線模塊控制來自控制模塊的多通道切換。 24個模擬信號中的一個被16位A/D轉換器選擇並轉換為數字信號。各通道信號採集完成後,將採集到的數據根據接收時序和握手信號通過三路可堆疊內部總數據傳輸至主控卡,再由FPGA統一幀主控卡的主控模塊,然後傳輸到內存完成數據的採集和存儲過程。

多路模擬開關的切換是數據採集卡的重要內容。本設計中,每塊數據採集卡需要同時採集24個不同頻率的模擬信號,因此需要高精度、準確地控制採樣通道地址的切換和選擇,對設計提出了很高的要求的硬件和軟件。硬件部分使用的模擬開關是adg706,是一個可以選擇16路信號的芯片。由於採集通道為24通道,每塊採集卡需要兩片adg706芯片,開關量達到16x2 = 32 > 24通道,滿足設計要求。

FPGA PCB設計

FPGA PCB的設計規模增大,IO傳輸問題也就出現。 為了相容其他高速模塊,必須對PCB的設計進行優化。

電源濾波,降低系統雜訊匹配訊號線降低並行走線的噪擾减小反彈效應進行阻抗匹配.

為了實現上述要求,可以採用的方法有:

1、選擇合適的資料,一般選用介電常數越小的資料,傳輸阻抗越小,傳輸損耗越小。 Altera中給出了FR-4的高速報告,說明FR-4可以跑高速設計。 但是,一般還是需要瞭解廠家的資料的資訊,用於整個設計的阻抗計算。

2、PCB上傳輸走線,有微帶傳輸線佈局單一參攷面、和帶狀傳輸線佈局雙參攷平面、兩種,可以支持基本的設計。

3、阻抗計算,在PCB板設計之初就做好阻抗的控制,保證後期有足够的時序餘量。

4、降低串擾和維持信號完整性的佈線方法

在允許範圍內,提高線距

臨近地線,可以去耦合

差分佈線,可以提高信號完整性

存在明顯耦合,可以在不同層之間佈設相互垂直的單端訊號這個現時不清楚咋做、

减小並線長度,减少長耦合走線

FPGA PCB電源供電

1、供電要求

單調性:帶電源爬升過程中單調非負斜率下降則為非正、,能够减小雜訊。

軟啟動:FPGA啟動時需要特定的電流,不能爬升的太快,每一級的電源達到預定狀態需要時間。

最大最小爬升時間:最大爬升時間是保證不會久留於閾值電壓附近,儘快達到邏輯電平。 最小爬升時間保證不會出現浪湧電流狀況。

敏感類比元件:需要穩定的電壓,不能有太大的電壓波動存在。 FPGA上的PLL就需要單獨的線性電壓源供電。

2、FPGA PCB的供電策略

電源層儘量靠近FPGA,可以减少BGA過孔電感,將Transceiver作為佈局最高優先順序高速收發器含有內部調製器、電流足够低、必須分配收發器關鍵軌道最高優先順序這三種情况除外、大電流電源軌道考慮:無高速收發器則大電流最高級,有則置於次優先順序核心電壓則可以放於最遠處、PLL電源及其他電源:PLL作為第三級考慮,其他電源按需分配。

FPGA PCB退耦電容

1、退耦電容的作用,利用電容的諧振頻率的極小範圍實現濾波,將雜訊去除。

2、計算電容值,實際電容的計算比較複雜,可以使用軟件自動計算。

3、電容的擺放,退耦電容最好的擺放就是盡可能的靠近電源或者地,保證最小的阻值和最小的感抗。

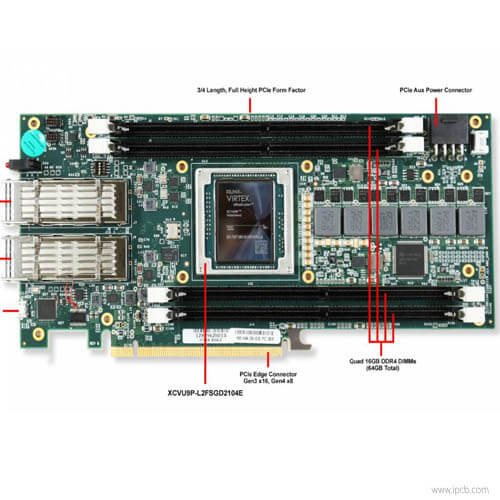

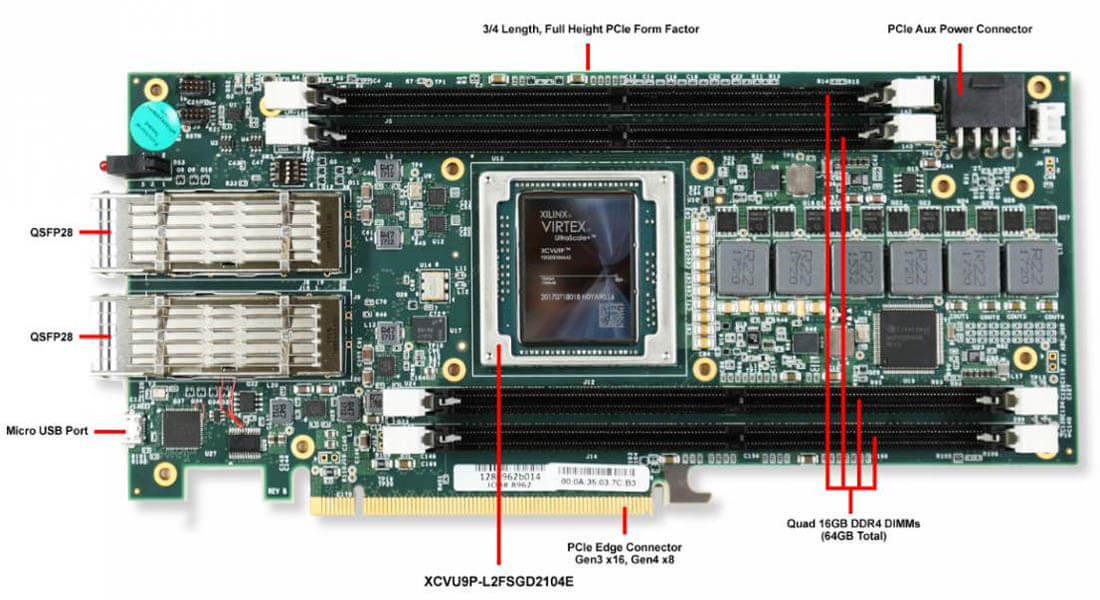

FPGA多數據採集卡PCBA

層數:12層

表面工藝 : 沉金

鍍金厚度:2U

PCB 顏色:綠色阻焊層

PCB測試:是

PCBA測試:是

提供PCB製造:是

iPcb 公司提供全套電子元件

PCBA 測試:是

符合 RoHS 的無鉛組裝

對於PCB技術問題,iPCB愛彼電路提供PCB技術的支持。 您也可以在這裡索取PCB報價或PCB諮詢。請聯繫郵箱: sales@ipcb.com

我們會非常迅速地做出回應。